# Bachelor Thesis Bachelor of Science Informatik

# Information Flow Analysis for CIL

Matthias Perner

TU Darmstadt Fachbereich Informatik

Prüfer: Prof. Dr.-Ing. Heiko Mantel Betreuer: Dipl.-Inform. Alexander Lux

Abgabetermin: 15. Oktober 2008

# Erklärung:

Hiermit versichere ich, dass ich die Arbeit selbstständig verfasst und keine anderen als die angegebenen Hilfsmittel und Quellen verwendet, sowie Zitate kenntlich gemacht habe.

Darmstadt, 15. Oktober 2008

Matthias Perner

#### Abstract

During program execution information flows exists between ressources. This flow can be restricted by flow policies to disallow public readable ressources to store data that is confidential.

In an information flow analysis, a program is checked for information flows that violate a given flow policy.

Security type systems are mechanisms to reduce the analysis to a typability problem.

In the theoretical part of this thesis, we develop a security type system for a subset of the Common Intermediate Language (CIL) that handles local information ressources and managed pointers to local information ressources.

In the implementation part of this thesis, we develop a prototypical checking tool that uses a security type system for a subset of the CIL that handles only local information ressources to analyse programs. CONTENTS CONTENTS

|   |        |   | 1         |   | 1            |

|---|--------|---|-----------|---|--------------|

|   | $\cap$ | n | ${ m te}$ | n | T C          |

| • | ι,     |   |           |   | $\mathbf{u}$ |

| 1     | Intr |                                                   | 5  |  |  |  |  |  |

|-------|------|---------------------------------------------------|----|--|--|--|--|--|

|       | 1.1  |                                                   | 5  |  |  |  |  |  |

|       | 1.2  |                                                   | 5  |  |  |  |  |  |

|       | 1.3  |                                                   | 6  |  |  |  |  |  |

|       |      | 1                                                 | 6  |  |  |  |  |  |

|       |      | 1.3.2 Stacks and Stackoperations                  | 6  |  |  |  |  |  |

| 2     | Bas  |                                                   | 7  |  |  |  |  |  |

|       | 2.1  |                                                   | 7  |  |  |  |  |  |

|       | 2.2  | v                                                 | 8  |  |  |  |  |  |

|       | 2.3  |                                                   | 9  |  |  |  |  |  |

|       | 2.4  | Soundness Proof                                   | 9  |  |  |  |  |  |

| 3     | CIL  | $v_{int}$ - Primitives and Local Ressources       | 0  |  |  |  |  |  |

|       | 3.1  | Memory Model and Program States                   | 0  |  |  |  |  |  |

|       | 3.2  | Instruction Set and Semantics                     | 0  |  |  |  |  |  |

|       | 3.3  | Non-Interference                                  | .1 |  |  |  |  |  |

|       | 3.4  | Typesystem                                        | 4  |  |  |  |  |  |

|       |      | 1 0                                               | 4  |  |  |  |  |  |

|       |      |                                                   | 6  |  |  |  |  |  |

|       |      | 3.4.3 Proof                                       | 8  |  |  |  |  |  |

| 4 Pro |      | ototypical Checking Tool                          |    |  |  |  |  |  |

|       | 4.1  | Requirements                                      | 9  |  |  |  |  |  |

|       |      | J                                                 | 9  |  |  |  |  |  |

|       |      | <u>U</u>                                          | 9  |  |  |  |  |  |

|       | 4.2  | 0                                                 | 9  |  |  |  |  |  |

|       |      | 0 1                                               | 20 |  |  |  |  |  |

|       |      | $\circ$                                           | 21 |  |  |  |  |  |

|       |      |                                                   | 22 |  |  |  |  |  |

|       | 4.3  | 0                                                 | 22 |  |  |  |  |  |

|       |      |                                                   | 22 |  |  |  |  |  |

|       |      | ·                                                 | 24 |  |  |  |  |  |

|       |      | v                                                 | 27 |  |  |  |  |  |

|       |      |                                                   | 8  |  |  |  |  |  |

|       |      |                                                   | 28 |  |  |  |  |  |

|       |      | 4.3.6 Overview of the Architecture                | 28 |  |  |  |  |  |

| 5     | Exa  | imple Analyses 29                                 |    |  |  |  |  |  |

|       | 5.1  |                                                   | 29 |  |  |  |  |  |

|       | 5.2  |                                                   | 0  |  |  |  |  |  |

|       | 5.3  | 1                                                 | 1  |  |  |  |  |  |

|       | 5.4  |                                                   | 2  |  |  |  |  |  |

|       | 5.5  | Example of a non-typable, non-interfering program | 3  |  |  |  |  |  |

| CONTENTS | CONTENTS |

|----------|----------|

|          |          |

| 6 $CIL_{pointer}$ - Basic Managed Pointers       3         6.1 Extension of the Memory Model and Program States       3         6.2 Instructionset and Semantics       3         6.3 Additional Pointer Information       3         6.4 Non-Interference       3         6.5 Typesystem       3         6.5.1 Abstract transformation       3         6.5.2 Proof       4         7 Conclusion       5         7.1 Summary       5         7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3 Additional Pointer Information       3         6.4 Non-Interference       3         6.5 Typesystem       3         6.5.1 Abstract transformation       3         6.5.2 Proof       4         7 Conclusion       5         7.1 Summary       5         7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                 |

| 6.4       Non-Interference       3         6.5       Typesystem       3         6.5.1       Abstract transformation       3         6.5.2       Proof       4         7       Conclusion       5         7.1       Summary       5         7.2       Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1       Requirements       5         B.2       Using PNIC       5         B.2.1       Quick Start       5         B.2.2       Main Menu       5         B.2.3       Submenu Flow Policy       5         B.2.4       Submenu Analysis Settings       5         B.2.5       Submenu Assemblies       5                                                                                                                |

| 6.5       Typesystem       3         6.5.1       Abstract transformation       3         6.5.2       Proof       4         7       Conclusion       5         7.1       Summary       5         7.2       Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1       Requirements       5         B.2       Using PNIC       5         B.2.1       Quick Start       5         B.2.2       Main Menu       5         B.2.3       Submenu Flow Policy       5         B.2.4       Submenu Analysis Settings       5         B.2.5       Submenu Assemblies       5                                                                                                                                                           |

| 6.5.1 Abstract transformation 3 6.5.2 Proof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.5.2 Proof       4         7 Conclusion       5         7.1 Summary       5         7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                      |

| 7 Conclusion       5         7.1 Summary       5         7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                  |

| 7.1 Summary       5         7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                               |

| 7.2 Related and Future Work       5         A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                           |

| A Task       5         B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B PNIC - Manual       5         B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B.1 Requirements       5         B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B.2 Using PNIC       5         B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.2.1 Quick Start       5         B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B.2.2 Main Menu       5         B.2.3 Submenu Flow Policy       5         B.2.4 Submenu Analysis Settings       5         B.2.5 Submenu Assemblies       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B.2.3       Submenu Flow Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B.2.4 Submenu Analysis Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B.2.5 Submenu Assemblies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B.3 Creating Flow Policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B.4 Creating Analysis Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B.5 CD Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C Proofs of Lemmas 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C.1 High Region Lemmas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C.1.1 High Level Regions Converge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C.1.2 No Visible Changes in High Regions 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C.1.3 High Regions Preserve Indistinguishability 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C.2 Virtual Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C.2.1 Virtual Steps Preserve Indistinguishability 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D Source Code of PNIC 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

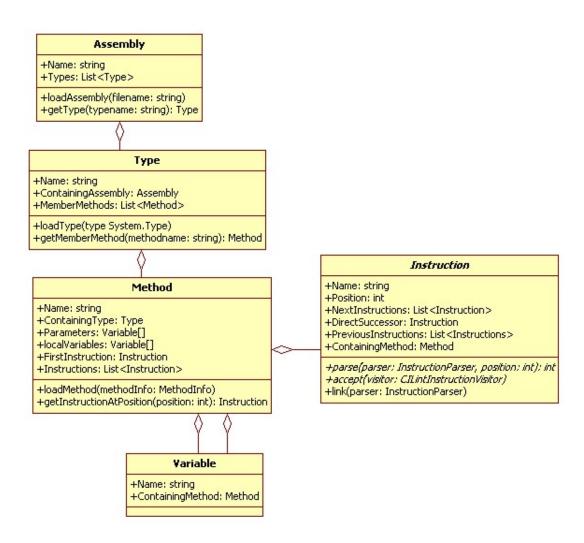

| D.1 Package Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D.1.1 File Analysis/AbstractState.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D.1.2 File Analysis/AnalysisSettings.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D.1.3 File Analysis/ControlDependencyRegion.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D.1.4 File Analysis/Flowpolicy.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D.1.5 File AST/Assembly.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

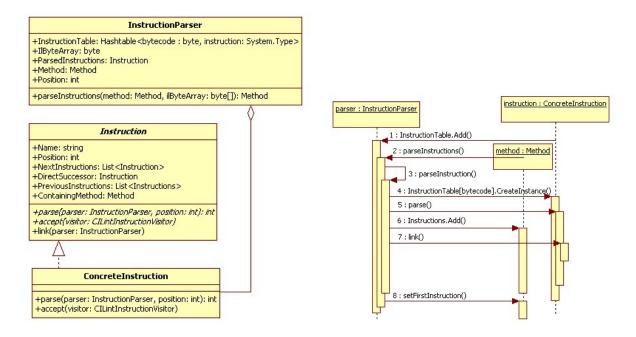

| D.1.6 File AST/Instruction.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D.1.7 File AST/CIL/CILintInstructions.cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CONTENT                         | CONTENTS CONTENTS                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D.:<br>D.:<br>D.:               | 1.9 File AST/CIL/BinaryInstruction.cs       99         1.10 File AST/CIL/Pop.cs       100         1.11 File AST/CIL/Push.cs       101         1.12 File AST/CIL/Load.cs       102         1.13 File AST/CIL/Store.cs       104                                                                                                             |

| D.<br>D.<br>D.<br>D.<br>D.      | 1.14 File AST/CIL/Unconditional Jump.cs       105         1.15 File AST/CIL/Conditional Jump.cs       106         1.16 File AST/CIL/Return.cs       110         1.17 File AST/InstructionParser.cs       110         1.18 File AST/Method.cs       113         1.19 File AST/Type.cs       116         1.20 File AST/Variable.cs       118 |

| D.:<br>D.:<br>D.:<br>D.:<br>D.: | 2.4 File Analysis/MethodTransformator.cs                                                                                                                                                                                                                                                                                                   |

| D.:                             | ckage View                                                                                                                                                                                                                                                                                                                                 |

## 1 Introduction

#### 1.1 Motivation and Goals

In our modern, heavily connected world many people and companies rely on software from third parties that may not be trustworthy. In other cases the original source of the software is unknown. This software often processes valuable or confidential information.

Furthermore, the software may communicate with the supplier or even another party for different reasons, e.g. registration, licensing or automated updates. As a result, it could be possible that these valueable and confidential information are leaked to a third party, either accidentally by bugs in the software, or even intentionally as a trojan horse. For these reasons, it is vital to check that the software in use is free of those leaks.

One way to ensure the absence of information leaks is a static information flow analysis. The intention of such an analysis is to look for those leaks in the program without running the software. Leaks can be distinguished in two types.

The first type are direct leaks, e.g. a secret information is assigned directly to a public visible ressource.

The second type are indirect leaks, e.g. a branching instruction has different execution paths depending on a secret constraint and assigns different values to a public ressource on each path.

It is possible to use a special kind of type system, a so called security type system, to find this kind of leaks. Such a type system is specific to one programming language. Therefore those type systems must be developed for every single language in use.

Furthermore, in many cases the user does not get the sourcecode, but only an executable in a low-level language. Nowadays, the executable is often written in some bytecode for a virtual machine, e.g. the Common Intermediate Language for the Virtual Execution System of the .NET-framework [ECM06]. Therefore it is essential to develop security type systems that can cope with those unstructured bytecode languages.

The goal of this work is to take a step on this road and develop such a type system for a subset of the CIL. Comparison of the bytecode language of the JVM [LY99] with the CIL suggests to use an existing type system for the JVM as base. Thus we use the type system in [BPR07] as fundament of the type system developed in this work. Furthermore, this work contains a proof that the type system really enforces the conditions described. Finally, a prototypical tool to run the analysis is developed to show that it is possible to use the type system in a semi-automated way.

#### 1.2 Structure of this work

This work consists of two major areas. A theoretical area and a practical area. The theoretical area starts with a short introduction and overview over the basic principles of security type systems in section 2.

Section 3 introduces a type system for a sublanguage of CIL, called  $CIL_{int}$ , which consists of the most basic operations in the CIL, like loading and storing of values to local variables and operations on primitive data types.

In section 4 we design and implement the type system for the  $CIL_{int}$  in form of a prototypical non-interference checking tool, to show that the theoretical analysis can be used for practical information flow checks.

In section 5 we analyse some example applications and examine the results of the analyses to evaluate the benefit of those type systems for practical software development and analysis.

In section 6 we introduce a type system for  $CIL_{pointer}$ . This sublanguage of the CIL is a superset of  $CIL_{int}$ , which expands the language with basic managed pointer operations, like address loading of local variables and indirect loading and storing of values to local variables. This part of CIL is most interesting, because many other bytecode languages do not support the direct use of pointers.

Finally we finish the work with a conclusion and an outlook to similar and future work in section 7.

#### 1.3 Conventions

During this work a lot of operations and notations are used that can not be assumed to be known by all readers, therefore it is essential to describe and define those notations to prevent missunderstandings.

#### 1.3.1 Replacements in Functions

Let  $f: A \to B$  be a function from set A to set B. Let  $a \in A$  and  $b \in B$ .

$f': f \oplus \{a \mapsto b\}$  describes the function that fulfils  $\forall x \in A : (x = a \Rightarrow f'(x) = b) \land (x \neq a \Rightarrow f'(x) = f(x)).$

That means f'(x) = f(x) for all values  $x \in A$  but a and f'(a) = b.

#### 1.3.2 Stacks and Stackoperations

Let A be a set. A stack of elements of the set A is of the type  $A^*$ . Let  $a \in A$  and  $as \in A^*$ . There are two possible operations on a stack:

**push** means that an element is added to the top of the stack. a :: as denotes the stack that results of a push a operation on the stack as.

**pop** means that an element is removed from the top of the stack. as denotes the stack that results of a pop operation on the stack a::as.

Furthermore let  $size: A^* \to \mathbb{N} \cup \{0\}$  be the function that returns the amount of elements on the stack and let as[i] denote the *i*th element on the stack.

# 2 Basics Principles

In this section we introduce security type systems with their most basic components. One foundation of security type systems are the flow policies, that describe which information flows are legal and which are illegal. The other basic foundation are the security conditions, which describe what the type system is intended to enforce.

## 2.1 Flow Policies

A flow policy consists of several distinct sets of information ressources, called security levels.

The flow policy itself is a partially ordered set of those security levels. A flow policy describes between which security levels a information flow is allowed. Information may flow from a security level to itself or to higher security levels. From now on let S be the set of all security levels in a given flow policy.

We introduce a shortcut to be able to retrieve the security level an information ressource is element of. This shortcut makes the definitions and proofs easier to read.

#### **Definition 1: Ressource Level**

Let SL(r) = sl, where r is an information ressource and sl is a security level, be the shortcut for  $r \in sl \in S$ .

Furthermore, we need to define the legal information flows using the partial order of the flow policy:

#### **Definition 2: Legal Information Flow**

If  $sl_1 \leq sl_2$ , then information may flow from  $sl_1$  to  $sl_2$ . If  $sl_1 \geq sl_2$ , then information may flow from  $sl_2$  to  $sl_1$ .

To formalize the illegal information flow, we change the definition of > and <. Instead of describing that a security level is higher, respectively lower than another, we use this operator to describe, that a security level is higher or not comparable, respectively lower or not comparable, than another.

#### Definition 3: <, >

```

Let < and > be relations of the type S \times S.

If (sl_1, sl_2) \in <, then (sl_2, sl_1) \in > and if (sl_2, sl_1) \in >, then (sl_1, sl_2) \in <.

<= \{s \in S \times S | s \notin \geq \}.

In the sequel sl_1 > sl_2 will be used insted of (sl_1, sl_2) \in > and sl_1 < sl_2 instead of (sl_1, sl_2) \in <.

```

With this information it is now possible to define illegal information flow on the base of < and >.

#### **Definition 4: Illegal Information Flow**

If  $sl_1 > sl_2$ , then no information may flow from  $sl_1$  to  $sl_2$ . If  $sl_1 < sl_2$ , then no information may flow from  $sl_2$  to  $sl_1$ .

During the analysis it will be necessary to determine the least upper bound of two security levels. The least upper bound can be defined as follows:

#### Definition 5: $\sqcup$

```

Let \sqcup be a partial function of the type S \times S \to S.

sl_1 \sqcup sl_2 = sl_3, where sl_1, sl_2, sl_3 \in S, if sl_3 \geq sl_1 \wedge sl_3 \geq sl_2 and \forall sl_4 \in S: if sl_4 \geq sl_1 \wedge sl_4 \geq sl_2, then sl_4 \geq sl_3.

```

One of the most simple flow policies, which is used through all this work, if not mentioned otherwise, is the policy which consists of the two security levels "low" and "high", where "high" is a higher security level as "low", denoted high > low and  $low \le high$ . That means data from information ressources of security level "low" may flow to any other information ressource, whereas data from information ressources of security level "high" may only flow to information ressources of security level "high".

This simple flow policy is adequate to model a great many of security requirements. For example lets have a look at an simplified email client: The user may have stored confidential information, like an adress book. For obvious reasons an email client needs a network interface. It is now essential to guarantee that any confidential information does not leave the email client via the network interface. With the simple flow policy it is possible to say that the network interface has the security level "low", whereas the confidential information has the security level "high". Therefore any confidential information may not leave the emailclient via the network interface, if the model fulfils the flow policies rules.

## 2.2 Security Conditions

If we want to develop an analysis it is good practice to formalize the properties of the application we want to check. This is done by the security condition.

Furthermore, an adequate formalisation of properties enables us to prove that an analysis enforces the properties we strive to fulfil. Therefore it is quintessential to find a security condition which formalizes the information flow rules we want to enforce.

In this work the security conditions used are called "non-interference" conditions. This term describes the fact that the visible output of a program depends only on the visible input. In other words, a program that is run several times with the same visible input produces the same visible output on every run, independent from any invisible input.

In combination with the flow policies it is now possible to define "visibility". Visibility depends on the possibilities of an observer and on the information ressources in use. Therefore it is possible to define the visibility of a ressorce as follows:

#### Definition 6: Visibility

Let  $sl_{obs}$  be the highest security level the observer is able to see.

An information ressource res is visibile to the observer, if  $sl_{observer} \geq SL(res)$ .

An information ressource res is invisible to the observer, if  $sl_{observer} < SL(res)$ .

## 2.3 Security Type Systems

The goal in this work is to develop a analysis to find illegal information leaks. Illegal information leaks are assignments of information, that depend on secret information, to public information ressources.

A security type system reduces the problem of finding those leaks to a typability problem. In this case, a type is a security level. To look if a program is typable, it is necessary to formalize the conditions on which a program is typable. This definition depends on the system developed and can be found in the section containing the type system.

In this work we will model the state of the runtime to observe the changes made by instructions as an abstract state. Using this abstract state, the rules for typability can be formalized as abstract transfer rules.

A program is typable using such a type system, if for every state of the runtime environment that is reachable by running the program an corresponding abstract state exists and an abstract transfer rule can be applied. Typability for the type systems developed is defined in the sections about the type systems, because the definition obviously depends on the definition of the abstract states and transitions.

## 2.4 Soundness Proof

The analysis of the program with the type system does only check, if a program is typable with this system. To ensure that a program that is typable does not violate the security conditions formalized, it is necessary to prove that typability implies the security conditions. This proof is called the soundness proof. This important part of the work will only be done for the more complex type system in section 6.

## 3 $CIL_{int}$ - Primitives and Local Ressources

In this section we introduce a subset of the Common Intermediate Language. It is the most basic subset containing only jumps and local integer variables. After introducing and explaining the language, we formalize the security conditions and develop a security type system for this subset.

The subset of the language is very close to the  $JVM_{\chi}$  from [BR05], therefore we can adapt almost the complete security type system introduced in their work.

## 3.1 Memory Model and Program States

A  $CIL_{int}$  program consists of an instruction list and local variables and parameters. All instructions in the instruction list must be part of the  $CIL_{int}$  sublanguage.

The local variables and parameters can be combined to a set  $\chi$ , because in the security type system local variables and parameters can be treated equally.

Furthermore we assign a number to every instruction in the list, called the program point. The program points can be used to identify instructions in a program. The first instruction in the list will be identified by 0, the second by 1 and so on. That means the set of program points consists of natural numbers including 0, denoted as  $PP = \{0, \ldots, n\}$ , where n is the amount of the instructions minus 1. In addition, let P[i] denote the instruction at program point i.

The state of the runtime environment can now be described by a triple  $\langle i, \rho, os \rangle$ , where  $i \in \mathbb{N} \cup 0$  is the next instruction to be executed,  $\rho \in \chi \rightharpoonup V$  is a mapping of local variables and parameters to values, where V is the set of primitive, native data types in the runtime environment, and  $os \in V^*$  is an operand stack, consisting of values from V. The combination of all states builds the set State.

Now it is possible to express the operational small step semantics, which describes the execution of each single instruction, as a relation that describes the state transitions of the runtime environment. The relation has the form  $\leadsto\subseteq State\times(State+V)$ .  $\leadsto^*$  denotes the transitive closure. Furthermore, we will use  $s_1 \leadsto^n s_2$  in the sequel, to denote that state  $s_1$  is transformed to state  $s_2$  in n steps.

Additionally, it is useful to introduce a shortcut function to note that a program evaluates to a specific value. From now on let  $P, \rho \downarrow v$  have the same meaning as  $\langle 0, \rho, \epsilon \rangle \sim^* v$ .

#### 3.2 Instruction Set and Semantics

As mentioned further above,  $CIL_{int}$  is the most basic instruction set. It consists of operation stack manipulating instructions, unconditional jumps and conditional jumps.

To reduce the amount of state transitions and at the same time reduce the amount of transfer rules needed for the type system, it is possible to merge some instructions in equivalence classes with respect to their stack transitions.

We use the following equivalence classes:

**unary** op Every instruction that pops one value from the operand stack, calculates a result by applying an unary function op to the value and pushes the result on the operand stack.

- **binary** op Every instruction that pops two values from the operand stack, calculates a result by applying a binary function op to those values and pushes the result on the operand stack.

- **pop** Every instruction that pops one instruction from the operand stack.

- **push** v Every instruction that pushes one constant value v on the operand stack

- **loadlocal** x Every instruction that loads the value of the local information ressource x on the operand stack.

- **storelocal** x Every instruction that pops a value from the stack and stores it in the local information ressource x.

- **jumpWith1Argument** t Every instruction that pops one value from the operand stack and passes control to either next instruction or target instruction P[t] based on the value.

- **jumpWith2Arguments** t Every instruction that pops two values from the operand stack and passes control to either next instruction or target instruction P[t] based on these values.

- **unconditionalJump** Every instruction that passes control to the target instruction P[t] instead of the next instruction.

- **return** Every instruction that exits the program and returns the top value of the operand stack.

The semantic of the different euqivalence classes is described in table 1.

#### 3.3 Non-Interference

As mentioned before, this work uses non-interference as security condition and it is vital to formalize the condition adequately. The goal of the analysis is to check if an illicit information flow exists in a program. The "non-interference" condition says: If a program is run several times with the same visible input, the visible output of the program is equal on every run. We want to develop a termination insensitive analysis, that means that the former conditions must only be fulfilled, if the program terminates.

With the definition of visibility in section 2.2 and the informal specification of non-interference, the necessity arises to define the indistinguishability of information, to be able to formalize runs with a combination of visible and invisible information.

It is obvious that the indistinguishability must depend on the maximum security level the observer is able to see, because this level determines which information ressources are visible. Furthermore, the condition must depend on the security levels of the information ressources, because those security levels determine the least security level an observer must have to be able to see the information ressource.

A special information ressource, when dealing with operand stack based languages, is the operand stack. It would not be accurate enough for the operand stack to be of

```

P[i] = unary \ op \quad op \in \mathbb{U} \quad op(v) = r

\langle i, \rho, v :: os \rangle \sim \langle i+1, \rho, r :: os \rangle

P[i] = binary \ op \quad op \in \mathbb{O} \quad op(v1,v2) = r

\langle i, \rho, v1::v2::os \rangle \sim \langle i+1, \rho, r::os \rangle

\frac{P[i]{=}pop}{\langle i{,}\rho{,}v{::}os\rangle{\leadsto}\langle i{+}1{,}\rho{,}os\rangle}

P[i]=push v

\overline{\langle i, \rho, os \rangle} \sim \langle i+1, \rho, v :: os \rangle

P[i] = loadlocal x

\overline{\langle i, \rho, os \rangle} \sim \langle i+1, \rho, \rho(x) :: os \rangle

P[i] = storelocal x

\overline{\langle i, \rho, v :: os \rangle} \sim \langle i+1, \rho \oplus \{x \mapsto v\}, os \rangle

\underline{cond1(v) = true} \quad \underline{P[i] = jumpWith1Argument} \quad t \quad cond1(v) = false

P[i]=jumpWith1Argument\ t

\langle i, \rho, v :: os \rangle \sim \langle t, \rho, os \rangle

\langle i, \overline{\rho, v :: os} \rangle \sim \langle i+1, \rho, os \rangle

P[i] = jumpWith 2 Arguments \ t \quad cond2(v1,v2) = true \quad P[i] = jumpWith 2 Arguments \ t \quad cond2(v1,v2) = false \quad

\langle i, \rho, v1 :: v2 :: os \rangle \sim \langle t, \rho, os \rangle

\langle i, \rho, v1::v2::os \rangle \sim \langle i+1, \rho, os \rangle

P[i] = unconditional Jump t

\langle i, \rho, os \rangle \sim \langle t, \rho, os \rangle

P[i] = return

\langle i, \rho, v :: os \rangle \sim v

where U denotes the set of unary functions,

O denotes the set of binary functions,

cond1 represents a function V \to \{true, false\}

cond2 represents a function V \times V \rightarrow \{true, false\}

v \in V, t \in PP and x \in \chi

```

Table 1: Semantic of  $CIL_{int}$

a specific security level, but it is possible to introduce a so called stack type  $st \in S^*$ , which is basically a stack of security levels. With the stack type it is possible to track the security levels of information on the operand stack according to their source.

Now it is possible to define indistinguishability relative to a security level  $sl_{obs} \in S$  and two stack types  $st, st' \in S^*$  and use this defintions to define the non-interference condition for the program. In the following definitions we will write  $\sim$  instead  $\sim_{sl_{obs}}$ , because there is no risk of confusion.

#### Definition 7: Indistinguishability of Values

Two values are indistinguishable, if they are equal.

$$\frac{v = v\prime}{v \sim v\prime}$$

## Definition 8: Indistinguishability of local Mappings

Two variable mappings  $\rho, \rho' \in \chi \to V$  are indistinguishable with respect to a security-level  $sl_{obs} \in S$ , if for every information ressource  $x \in \chi$  either x is mapped to equal values in both mappings or the security level of x is higher than sl.

$$\frac{\forall x \in \chi : \rho(x) = \rho'(x) \lor SL(x) > sl_{obs}}{\rho \sim \rho'}$$

## Definition 9: Indistinguishability of Operand Stacks

Two operand stacks are indistinguishable with respect to a security level  $sl_{obs} \in S$  and two security level stacks  $st, st' \in S^*$  with the same size as  $os, os' \in V^*$ , if they have equal size and every value on the stack is either equal or the corresponding security level on the security level stack is higher than  $sl_{obs}$ . Therefore it can be defined inductively:

$$\frac{size(os) = size(st) = size(st') = size(os') = 0}{os \sim_{st,st'} os'}$$

$$\frac{size(os) = size(st) = 0 \land os \sim_{st,st'} os' \land sl_v > sl_{obs}}{os \sim_{st,sl_v::st'} v :: os'}$$

$$\frac{os \sim_{st,st'} os' \land v = v' \land sl_v \leq sl_{obs}}{v :: os \sim_{sl_v::st,sl_v::st'} v' :: os'}$$

$$\frac{os \sim_{st,st'} os' \land sl_v > sl_{obs} \land sl'_v > sl_{obs}}{v :: os \sim_{sl_v::st,sl'_v::st'} v' :: os'}$$

#### Definition 10: Indistinguishability of States

Two runtime states are indistinguishable with respect to  $sl_{obs} \in S$  and  $st, st' \in S^*$ , if the variable mappings  $\rho, \rho' \in \chi \rightharpoonup V$  and operandstacks  $os, os' \in V^*$  are indistinguishable.

$$\frac{\rho \sim_{sl_{obs}} \rho' \wedge os \sim_{st,st'} os'}{\langle i, \rho, os \rangle \sim \langle i', \rho', os' \rangle}$$

Using these definitions it is now possible to formalize the non-interference condition for a program.

## Definition 11: Non-Interfering $CIL_{int}$ Program

A program P is non-interfering, if for every two local maps  $\rho$  and  $\rho'$ , where  $\rho \sim \rho'$ , the result v of a run of the program is equal.

$$\frac{\forall \rho, \rho' \in \chi \rightharpoonup V : \rho \sim \rho' \land P, \rho \Downarrow v \land P, \rho' \Downarrow v' \Rightarrow v = v'}{P \ is \ non-interfering}$$

## 3.4 Typesystem

## 3.4.1 Control Dependency Regions

One problem when dealing with low-level languages is handling branching instructions. At a branching instruction the control may be passed to different instructions, depending on loaded values. In consequence, those instructions are a possible reason for information leaks, when the condition of such an instruction depends on values of a high security level and in the two branches different assignments to a variable of a low security level are made.

In the following examples let lv be a variable of the security level "low" and hv be a variable of the security level "high". The flow policy in use is the simple high-low policy.

```

00 loadlocal hv

01 jumpWith1Argument 05

02 push 0

03 storelocal lv

04 unconditionalJump 07

05 push 1

06 storelocal lv

07 loadlocal lv

08 return

```

This program is obviously interfering, because looking at the return value is enough to learn something about the high level variable hv.

This problem can be addressed with control dependency regions. A control dependency region is an over approximation of the influence area of a branching instruction.

Let BP be the set of all branching points of a program. For  $CIL_{int}$  the set of branching points can be written as  $BP = \{i \in PP | (P[i] = jumpWith1Argumentt \lor P[i] = jumpWith2Argumentst) \land t \neq i+1\}.$

Let CDR be the set of control dependecy regions. CDR is modeled in form of two functions:

```

junction: BP \rightarrow PPregion: BP \rightarrow \mathcal{P}(PP)

```

The set region(i) models the program points of instructions that may be visited on either branch of the control flow after the branching instruction P[i].

The partial function junction(i) models the program point at which both branches of the control flow converge. It is a partial function, because it is possible that the control flow paths do not converge after a branching, as shown in the following simple example:

```

00 loadlocal lv

01 jumpWith1Argument 03

02 return

03 return

```

To model the control dependency regions as an safe over approximation of the influence areas, it is important to formalize conditions for a safe over-approximation that allows us to guarantee that the secret guard in the condition does not have influence on information ressources outside its control dependency region.

Let  $\mapsto \in PP \times PP \cup \{-1\}$  be the successor relation. It is defined by:

- 1. if P[i] = unconditional Branch t, then  $(i, t) \in \mapsto$

- 2. if P[i] = jumpWith1Argument t, then  $(i, i + 1) \in \mapsto$  and  $(i, t) \in \mapsto$

- 3. if P[i] = jumpWith2Arguments t, then  $(i, i + 1) \in \mapsto$  and  $(i, t) \in \mapsto$

- 4. if P[i] = return, then  $(i, -1) \in \mapsto$ , expressing that return has no successor in the program.

- 5. else  $(i, i+1) \in \mapsto$

## Definition 12: Safe Over Approximation

A control dependecy region must fulfil the following three conditions:

1. for all program points i and all their succesors j, k that fulfil  $j \neq k$  (that means i is a branching instruction and therefore  $i \in BP$ ), either  $k \in region(i)$  or k = junction(i)

$$\forall i, j, k \in PP : i \mapsto k \land i \mapsto j \land j \neq k \Rightarrow k \in region(i) \lor k = junction(i)$$

2. for all program points i, j, k, that fulfil  $j \in region(i)$  and  $(j, k) \in \mapsto$ , either  $k \in region(i)$  or k = junction(i)

$$\forall i, j, k \in PP : j \in region(i) \land j \mapsto k \Rightarrow k \in region(i) \lor k = junction(i)$$

3. for all program points i, j, that fulfil  $j \in region(i)$  and P[j] = return, junction(i) must be undefined

$$\forall i, j \in PP : j \in region(i) \land P[j] = return \Rightarrow junction(i) \text{ is undefined}$$

The first condition ensures that every instruction, that is a direct successor of a branching instruction is either in the region or the junction of the branching instruction and thus is in the control dependency region of the branching instruction.

The second condition ensures that every instruction that is a direct successor of an instruction in the region of a branching instruction is either in the region or is the junction of the branching instruction and thus is in the control dependency region of the branching instruction.

The third condition ensures that in presence of a return in the region of a branching instruction the junction of the branching instruction is undefined. That is important, because if a return exists in the region of a branching instruction the control flow of different branches can not converge after the return.

#### 3.4.2 Abstract Transformation

The analysis consists of a set of abstract transfer rules that manipulate an abstract state. Thus it can be seen as an abstract interpretation. This means that the analysis is an approximate run of the program. It ignores all information that is not of interest for the analysis. In the security type system the only interesting information are the security levels of information ressources. Therefore these are the only information we need to model in the abstract state.

Let ST be the set of stacks of security levels  $S^*$  and SE be the set of functions  $PP \to S$ . The analysis can now be described as transfer rules for tuples of the type  $(st, se) \in ST \times SE$ . st is called the security level stack and represents the security levels of values on the operand stack. se is called the security environment and represents the least upper bound of security levels of all regions the instruction is part of and therefore the least upper bound of all guards the instruction is executed under.

Furthermore we need a pointwise extensions of  $\sqcup$  to be able to use it on security environments and stack types. This functions can be defined as follows:

## Definition 13: $lift_{sl}$

Let  $lift_{sl}$ , where  $sl \in S$ , be a function of the type  $ST \to ST$ . If  $st' = lift_{sl}(st)$ , then:

$$size(st) = size(st') \land \forall i \in \{n \in \mathbb{N} | n \le size(st)\} : st'[i] = st[i] \sqcup st$$

Let  $lift_{sl}$ , where  $sl \in S$ , be a function of the type  $SE \times region \rightarrow SE$ . If  $se' = lift_{sl}(se, region(i))$ , then

$$\forall j \in PP : (j \in region(i) \Rightarrow se'(j) = se(j) \sqcup sl) \land (j \not\in region(i) \Rightarrow se'(j) = se(j))$$

Now it is possible to define the abstract transfer rules that manipulate the abstract state. These rules can be found in table 2.

It is obvious that the store is only allowed, if the value on the stack may flow to the security level of the variable or paramter. Furthermore, the loading rules push values on the stack and push the least upper bound of security levels of all information ressources that influence the new value on the stack type. Finally, the rule for program termination with return can only be applied, if the security environment of the instruction is low and the value on top of the stack is low.

After introducing the abstract transfer rules it is now necessary to define the typability of a program. In the introduction we said that a program is typable, if for every state of the runtime environment, that is reachable by running the program, a corresponding abstract state exists and an abstract transfer rule can be applied.

$$P[i]=unary\ op$$

$$i\vdash sl::st,se\Rightarrow sl\sqcup se(i)::st,se$$

$$P[i]=binary\ op$$

$$i\vdash sl_1::sl_2::st,se\Rightarrow sl_1\sqcup sl_2\sqcup se(i)::st,se$$

$$\frac{P[i]=pop}{i\vdash sl_1::st,se\Rightarrow st,se}$$

$$\frac{P[i]=push\ v}{i\vdash st,se\Rightarrow se(i)::st,se}$$

$$\frac{P[i]=loadlocal\ x}{i\vdash st,se\Rightarrow sL(x)\sqcup se(i)::st,se}$$

$$\frac{P[i]=stloc\ x\ SL(x)\geq sl_1\sqcup se(i)}{i\vdash sl_1::st,se\Rightarrow st,se}$$

$$\frac{P[i]=sunconditional\ Jump\ t}{i\vdash sl_1::st,se\Rightarrow lift_{sl_1}(st),lift_{sl_1}(se,region(i))}$$

$$\frac{P[i]=jump\ With\ 2argument\ t}{i\vdash sl_1::sl_2::st,se\Rightarrow lift_{sl_1\sqcup sl_2}(st),lift_{sl_1\sqcup sl_2}(se,region(i))}$$

$$\frac{P[i]=return\ sl_1\sqcup sl_2(se,region(i))}{i\vdash sl_1::sl_2::st,se\Rightarrow}$$

where  $lsl\in S$  is the least security level of the flow policy,  $v\in V,\ t\in PP$  and  $x\in \chi$

Table 2: Abstract transferrules for  $CIL_{int}$

It is obvious that this informal definition requires a defintion for "corresponding states". This can be defined as follows:

#### Definition 14: Corresponding States

An abstract state  $st_i, se_i \in ST \times PP \to S$  corresponds to a runtime state  $\langle i, \rho_i, os_i \rangle$ , if both are either the initial states  $\langle 0, \rho, \epsilon \rangle$  and  $\epsilon, se$  of a program or if the states result from two corresponding states by applying a semantic rule and an abstract transfer rule.

$$\frac{st_{i}, se_{i} = \epsilon, se \quad \langle i, \rho_{i}, os_{i} \rangle = \langle 0, \rho_{0}, \epsilon \rangle}{\langle i, \rho_{i}, os_{i} \rangle \parallel st_{i}, se_{i}}$$

$$\underline{st_{j}, se_{j} \Rightarrow st_{i}, se_{i} \quad \langle j, \rho_{j}, os_{j} \rangle \leadsto \langle i, \rho_{i}, os_{i} \rangle \quad \langle j, \rho_{j}, os_{j} \rangle \parallel st_{j}, se_{j}}}{\langle i, \rho_{i}, os_{i} \rangle \parallel st_{i}, se_{i}}}$$

Now that corresponding states are defined, it is possible to define the typability using the corresponding states. For the transition of abstract states we write  $\rightarrow$  instead of  $\Rightarrow$  in this definition to prevent confusion.

## Definition 15: $CIL_{int}$ Typeablility

A program P is typable, if for the last runtime state before terminating a corresponding abstract state exists and an abstract transfer rule can be applied.

$$\frac{\forall v \in V : P, \rho \Downarrow v \Rightarrow \langle 0, \rho, \epsilon \rangle \leadsto^* \langle i, \rho_i, v :: os_i \rangle \leadsto v \land st_i, se_i \to \land \langle i, \rho_i, v :: os_i \rangle \parallel st_i, se_i}{p \ is \ typable}$$

It is now possible to proof that all typable programs fulfil the non-interference condition in the soundness proof.

#### 3.4.3 **Proof**

The soundness proof for this type system can be done as an induction on the length of executions. The basic idea is to proof that a program that is run with indistinguishable input preserves the indistinguishability during the whole length of the execution. That means that invisible instructions do not change visible information ressources and visible instructions preserve the indistinguishability of states. The first claim is necessary, because changes in low level information ressources in a high level region may leak information about the guard. The second claim is necessary, because if a visible instruction violates this claim, it is possible, that low level information ressources get different values assigned and therefore the indistinguishability of the output could be violated.

The proof is left to the interested reader, because later in this work is a proof for the  $CIL_{pointer}$  type system, which is more complex and contains the proof for the  $CIL_{int}$  system, because  $CIL_{pointer}$  is a superset of  $CIL_{int}$  and the abstract transfer rules of the type system for  $CIL_{pointer}$  contain the typability conditions of the  $CIL_{int}$  type system.

# 4 Prototypical Checking Tool

After developing the theoretical type system for  $CIL_{int}$ , it is interesting to show a possibility how to implement such a type system to show that the theoretical foundations make it possible to automatically check binaries for illicit information flow. This section describes the decisions made during the development of a prototypical checking tool for  $CIL_{int}$ . The source code of this tool can be found in appendix D.

## 4.1 Requirements

A checking tool should fulfil some requirements, which can be differentiated into functionality and extendability.

## 4.1.1 Functionality

One reason for implementing the tool is to show that it is possible to implement the theoretical analysis in a way that correctness is guaranteed, if the tool accepts the program as valid. Correctness can only be guaranteed, if every unexpected result is interpreted as failure of the analysis. Furthermore, every condition must be checked exactly as the definitions and claims of the theoretical model and analysis demand.

Another reason to implement the prototypical checking tool is to show that it is possible to implement a tool that does those checks semi-automatically, even in the case that the source code is not available for analysis. Therefore the prototypical checking tool shall not operate on a textual representation of programs, but on assembly files instead. In this case, assembly files are portable executables that contain managed CIL code.

#### 4.1.2 Extendability

$CIL_{int}$  is only a small part of the complete CIL, therefore it is important to design the tool with a focus on extendability. If the program is easy to extend, then it will be possible in to use the implementation in further works that analyse greater sublanguages of CIL. Therefore it is necessary to design the parser, the program and memory model and the analysis extendable. It must be easy to add more instructions to the parser. The program and memory model must support adding information that are needed for more complex CIL sublanguages to them easily. The analysis needs to be adaptable to those more complex models.

## 4.2 Work Flow and Program Behaviour

It is useful to define the program behaviour in a way that the work flow for using the program is comprehensible for the user. This can be done by looking at the setup process for the analysis and the course of actions during the analysis.

## 4.2.1 Setting up the analysis

- 1. Defining security levels and a flow policy that is to be used during the next analysis

- 2. Choosing the methods to check. That includes choosing the assemblies and types that include the methods.

- 3. Assigning security levels to the information ressources, that means variables and parameters.

- 4. Running an analysis.

From this setup process it is possible to draw several conclusions. The first important conclusion is that it would be useful to use files to save the setup settings of an analysis, because it is a complex process and the user should be spared of doing it multiple times, if a further run of the analysis is necessary.

Furthermore, it is obvious that the flow policies can be used through several different analyses. As a result it is reasonable to save the flow policy in a different file than the settings of an analysis.

The assignment of security levels, however, is not indepedent of the methods that are the targets of the analysis. Therefore it is useful to store those settings in one common file.

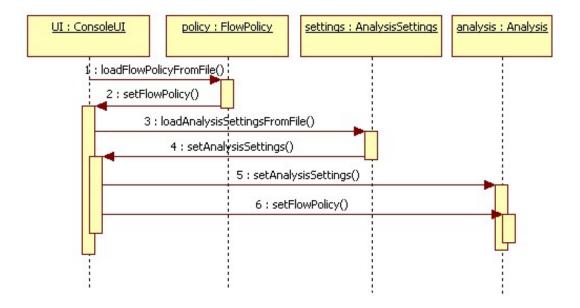

This results in the setup process for an analysis in the program shown in figure 1.

Figure 1: Setup process of an analysis

One could argument, that the security levels are not independent from the flow policy, too, but that problem can be addressed, by checking if the flow policy in use and the

settings file in use are compatible before running the analysis. By doing so it is possible to handle the settings needed for an analysis and the flow policy that is used in the analysis indepedent and thus improve the reuseability of the settings and flow policies.

## 4.2.2 Course of actions during analysis

- 1. For every assembly to analyse

- (a) Open assembly

- (b) For every type and method to check

- i. Analyse the recent method

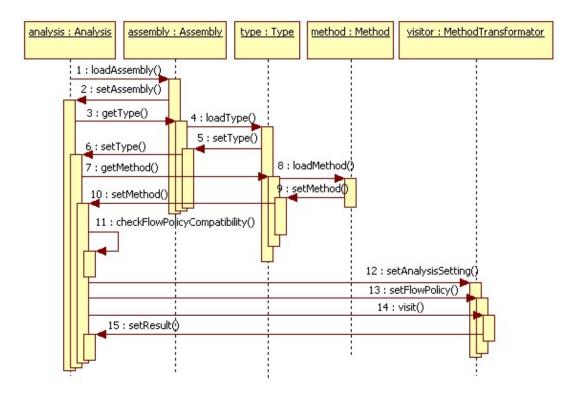

The most important conclusion to draw from this course of actions is the insight that it is helpful to present the result of an analysis, before running the next analysis and, after all analysis runs are done, presenting a summary of all runs. This results in the sequence of actions during a single method analysis shown in figure 2.

Figure 2: Running an analysis on a single method

#### 4.2.3 User Interface Behaviour

When starting the application the main menu shows up. From this menu it is possible to change into the submenus for the flow policy, the analysis settings and assemblies. Furthermore, it is possible to run an analysis from this menu.

In the flow policy menu, it is possible to load a flow policy. If the flow policy file given is not valid, the program requests a new filename. Furthermore it is possible to dump the flow policy to the console.

In the analysis settings menu, it is possible to load settings from a file. Additionally it is possible to dump the settings to the console. It is possible, to initialize an analysis settings file. When selecting this action, the user is asked for a name for the new file. If the file already exists, the program asks for another file name. After a valid file name is given, the user is prompted for assemblies to analyze, until an empty line is entered. The program creates a new file with the given filename, adding all the types and methods, including their variables and parameters to the newly created file.

In the assembly menu, it is possible, to load an assembly and to dump it to the console. If the file is not a valid managed code assembly, the program does not load the file.

When running an analysis, the first action of the program is to check if the flow policy and the analysis settings are compatible. If this check is successful, the analysis is started. After analysing a method the result is printed to the console, if the method is interfering the instruction list is shown to make it easier to find the problematic instructions. After all methods are checked, a summary is presented, that states if the methods are non-interfering and in case a method is not non-interfering the reason is given.

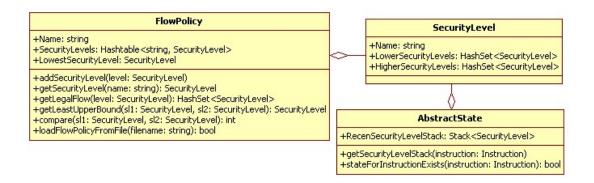

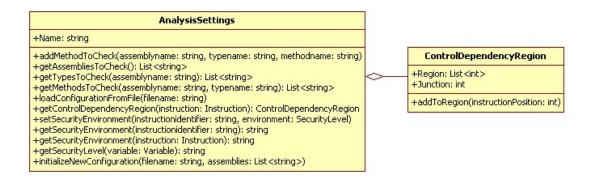

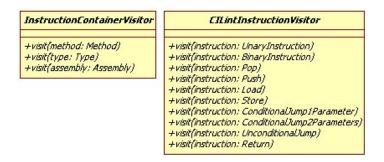

## 4.3 Design