RiCaSi Toolchain

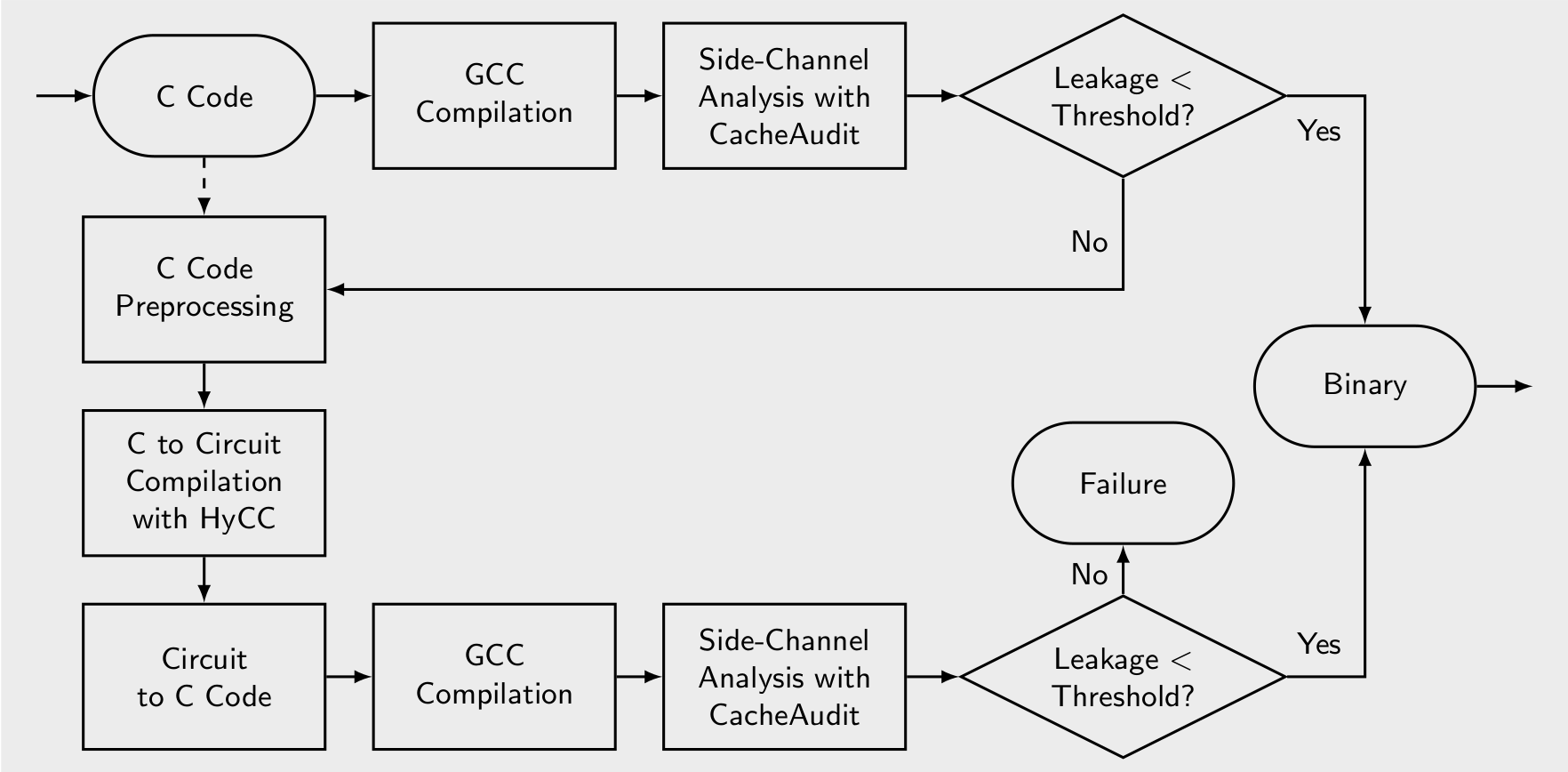

Cache side channels constitute a persistent threat to crypto implementations. Implementing crypto as software evaluations of circuits avoids this threat but is very costly. RiCaSi combines program analysis and circuit compilation to support the selective hardening of regular C implementations against cache side channels.

RiCaSi avoids unnecessary complexity and overhead if it can derive sufficiently strong security guarantees for the original implementation. If necessary, RiCaSi produces a circuit-based, hardened implementation. For this, it leverages established circuit-compilation technology from the area of secure computation. A final program analysis step ensures that the hardening is, indeed, effective.

Publication

Heiko Mantel, Lukas Scheidel, Thomas Schneider, Alexandra Weber, Christian Weinert and Tim Weißmantel.In International Conference on Cryptology and Network Security (CANS), pages 505-525, 2020.

[ BibTeX entry | PDF | Video Presentation ]

[ BibTeX entry | PDF | Video Presentation ]

Overview of the Tool

Downloads and Supplementary Material

- Side-Channel Analysis: Download

- Non-circuit binaries of case-study implementations: Download

- HyCC circuit compiler: GitLab

- Circuit-to-C Converter: Download

- Circuit-based C code of case-study implementations: Download

- Circuit-based binaries of case-study implementations: Download